# A Discussion on Accurate Phase or Time Synchronization Techniques for the Aerospace Control Systems

## Eloy Martins de Oliveira Junior

### Marcelo Lopes de Oliveira e Souza

INPE, Av. dos Astronautas, 1754, eloy@dem.inpe.br<sup>1</sup>, marcelo@dem.inpe.br<sup>2</sup>

Abstract: Current systems such as satellites, aircrafts and traffic controls are becoming increasingly complex and/or highly integrated as prescribed by the SAE-ARP-4754 Standard. The requirements of such systems, as clock speed, high-performance and high-integration, are increasing rapidly. Therefore, techniques to reduce phase or time de-synchronization caused by the environment disturbances, environment variability, plant nonlinear dynamics, plant wear, plant faults, or the non-symmetric plant operation, become an important issue for the conception and design of such systems. This paper presents a discussion on accurate phase or time synchronization techniques for the aerospace control systems. It is based on the review of the literature, discussion and simulation of one PLL (Phase Locked Loop) technique used in an aerospace control system which require phase or time synchronization among simultaneous rotor units. The preliminary results of such discussion shows that the PLL technique used: 1) can reduce the phase skew between two distinct controls; 2) can contribute to high levels of performance and reliability of aerospace control systems.

Keywords: Synchronization, PLL, Control System, time synchronization, phase synchronization.

#### 1 Introduction

Current systems such as: satellites, aircrafts and traffic controls are becoming increasingly complex and/or highly integrated as prescribed by the SAE-ARP-4754 Standard. In accordance to Meyr and Ascheid (1990) and Hsieh and Hung (1996), the requirements of such systems, as clock speed, high-performance and high-integration, are increasing rapidly. Therefore, techniques to reduce phase or time de-synchronization caused by the environment disturbances, environment variability, plant non-linear dynamics, plant wear, plant faults, or the non-symmetric plant operation, which are the space environment characteristics, becomes an important issue for the conception and design of such systems. Therewith, the synchronization problem in phase or time appears in many domains as aerospace controls. Nevertheless, according to Meyr and Ascheid (1990), there is an impression that the synchronization task is a trivial one, but this is an unfortunate misconception. Sometimes, the synchronization task in phase or time becomes critical in the framework of complex and/or highly integrated systems. The PLL (Phase Locked Loop) is one of the most known techniques to achieve an accurate and fast phase or time synchronization.

According to Hsieh and Hung, the PLL (Phase-Locked Loop) technique emerged in mid-1923 and in accordance to Kihara *et al.* it has four major applications:

- the synthesizer;

- the filter resonator;

- the demodulator;

- the automatic control system;

All these applications are useful for establishing coherent phase or time references, jitter reduction, skew suppression, frequency synthesis, jitter and clock recovery among numerous systems such as on-chip systems, wireless communication systems, digital communication circuits, low power clock generation, motion control systems, navigation, computing, control of vehicles and others.

According to Djamito and Sutopo, DC (Direct Current) motors are simple to control, what can be achieved conventionally by an analog servo feedback. Further, they have been widely used in aerospace applications.

Thus, this paper aims to show an discussion on accurate phase or time synchronization techniques for the aerospace control systems. This discussion is based on the review of the literature, discussion and simulation of one PLL technique used in a DC motor control system which requires phase synchronization among two distinct DC motor control loops due to environment variability. In other words, this paper intends to show that the PLL technique can be used not only to synchronize a single DC motor control loop, but also for phase synchronization between two distinct control loops. To achieve this goal, a second-order DC motor is used as a plant, subjected to a combination of two modes of control: 1) The proportional, integral, and derivative (PID)

one; 2) The PLL one. In this scheme, we expect that: 1) The PID controller acts on a plant to maintain the speed reference; 2) The PLL controller acts on a plant to maintain the phase synchronization between the existing control loops. Thus, it is possible to synchronize the angular motion among DC motor loops.

Finally, the model proposed above was simulated using the Matlab/Simulink environment and the results were analyzed.

#### 2 The Synchronization Problem

The phase or time synchronization is essential in meeting the demands of real-time critical control systems. According to Suri *et al.*, a variety of system models and synchronization techniques exist in the current literature. However, to correctly understand and to ignore unnecessary details and focus on the essential features of the design, abstractions are necessary. Abstractions are often applied in a hierarchical fashion, where each layer of abstraction relies on the essential features of the abstraction level below, and hides unessential details from the lower level. Many models of abstractions are possible, depending on the circumstances. To better understand, we divided them into three main abstraction layers: physical, hardware, and software; as shown in Figure 1.

Figure 1 - Main Abstraction Layers.

Figure 1 shows the following main abstraction layers:

- Physical representation is the layer where we have physical materials and properties, e.g. quartz crystal.

- Hardware representation is the layer where we have the oscillator mechanism(s).

- Software representation is the layer where we have the logical time(s), i.e., the time(s) controlled by software.

Many solutions have been devised to provide the various levels of granularity to coordinate systems among the three main abstraction layers. So, in this paper, we present an discussion of phase or time synchronization techniques which demands a hardware solution used in a DC motor control system which require phase or time synchronization among two distinct DC motor control due to environment variability.

### 3 Phase locked loops

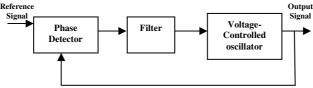

The basic PLL configuration block diagram consists of a phase detector, a loop filter and a voltage controlled oscillator as shown in Figure 2. Even complex PLLs share this configuration.

Figure 2. Basic PLL Configuration.

The characteristics of complete PLLs depend on their elements. Moreover, since the PLL output is synchronized to the input signal (reference signal); the characteristics of the input signal also influence PLL performance, according to Hsieh and Hung.

#### 3.1 Phase Detector

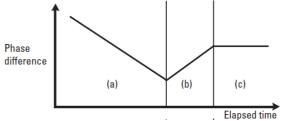

The phase detector block measures the difference in phase between the output signal and the reference signal. Figure 3 shows an example of a phase difference that change over time, during the phase synchronization process. The three steps shown: (a) is the initial condition, i.e., when the PLL do not begin to actuate on the loop yet; (b) is the transition, i.e., when the PLL control begins the actuation on the loop; (c) is the steady state

condition, i.e., when the PLL control achieve the phase synchronization between the output and the reference signals.

Figure 3. Phase Difference: (a) initial condition, (b) condition between the first and second digital controls, and (c) condition after the control.

Source: Kihara et al.

#### 3.2 Filter

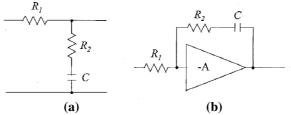

A low-pass filter is generally used in PLL controllers to suppress undesirable high-frequency components and noise, which are not used in phase synchronization.

Figure 4, according to Hsieh and Hung and Djamito and Sutopo, shows first order passive and active filters used in PLL applications.

Figure 4. (a) Passive Filter. (b) Active Filter. Source: Hsieh and Hung.

#### 3.3 Voltage Controlled Oscillator

The most significant difference between a PLL and passive devices, such as filters, is that the PLL has an active internal signal source: the oscillator. Thus, the PLL does not directly deliver a processed form of the signal it receives, but it generates its own signal instead. The oscillator frequency has to be changed so as to synchronize it to the input signal of the PLL, and the output phase of the controlled oscillator must be synchronized to the input signal (Kihara *et al.*).

According to Hsieh and Hung, the main requirements to establish a good voltage controlled oscillator are:

- phase stability;

- large frequency deviation;

- high modulation sensitivity;

- linearity of frequency versus control voltage;

- capability for accepting wide-band modulation.

The phase stability opposes itself directly to the other four requirements. To achieve the phase stability, a tradeoff among the requirements is necessary.

### 4 Design of Simulations

### 4.1 Two DC Motor Control LOOPS with PLL

The DC motor was chosen because it is widely used in many aerospace applications, and also due to the many researches with PLL related in the literature as in Kihara *et al.*, Djamito and Sutopo, Machida and Kobayashi.

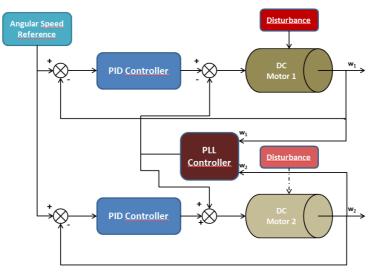

Most applications have used the PLL to control motion and phase synchronization in one DC motor loop. This paper synchronizes the angular speed and the angular position between two independent DC motors control loops in the presence of environment variability represented by disturbances in loops. The disturbance changes the phase of an angular motion inducing the phase de-synchronization between the loops. In this paper, we analyze and simulate the case shown in Figure 7.

In Figure 7 each DC motor is controlled by a PID (Proportional, Integrative and Derivative) controller. Each PID controller is responsible for maintaining the DC motor in agreement with the external reference signal, which is the same for both loops.

Figure 7. DC motor model with PLL between loops.

The disturbances can be interpreted as loads to DC motors; i.e., the disturbances, in this paper, are constants. The disturbances cause bumps in the DC motors and reduce their angular speeds inducing a skew in angular speed and angular position between loops. Therefore, the angular speeds and angular positions of DC motors are desynchronized in this instant. We add a PLL controller between the loops. The PLL observes and acts: 1) to improve the response of the system to maintain the angular speed synchronized between loops; and 2) to maintain the angular position synchronized in phase between loops. To do that, the PLL observes the skew of phase and actuates in the loops to synchronize the phases of angular motions and, in consequence, the angular speeds and angular positions.

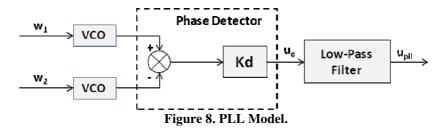

The Figure 8 shows the basic block diagram of transfer functions of the PLL used in the simulations. It is possible to observe the phase detector, filter and VCO that are described below.

where:

- w1 Angular speed of DC motor loop 1;

- w2 Angular speed of DC motor loop 2;

- Kd proportional constant of phase detector;

- upll control law of PLL.

The equations below, based on Kihara *et al.*, and Djamito and Sutopo, describe a linear mathematical model of a PLL used to perform the simulations.

The angular speeds of the loops are the inputs to the VCOs (Voltage Controlled Oscillators). A VCO generates oscillations due to the angular speed. Based on Kihara *et al.* and Djamito and Sutopo, the transfer function of a VCO is given by:

$$K_{v} = \frac{K_{vco}}{s} \tag{1}$$

Where KVCO is the gain of a VCO.

The phase detector measures the phase difference of output signals of VCOs.

$$\Delta \theta = \theta_i(t) - \theta_0(t) \tag{2}$$

In Equation 2,  $\Delta\theta(t)$  is the phase difference between the signals;  $\theta$ i is the phase related to input signal 1 (angular speed of DC motor 1); and  $\theta$ o is the phase related to input signal 2 (angular speed of DC motor 2).

According to Djamito and Sutopo, the output signal of the phase detector is composed by DC components and harmonics, which will be eliminated by the low-pass filter. So, for small phase differences, the linearized transfer function of the phase detector may be considered as a constant, as shown in equation 3:

$$K_d = \frac{V_d}{\theta_i(s) - \theta_0(s)} \tag{3}$$

The output signal of the phase detector is filtered by a low-pass filter to suppress the noise and undesirable frequencies. In this paper we use an active filter, as shown in Figure 4.

Based on Kihara et al., Djamito and Sutopo, the closed-loop transfer function of the active filter is given by:

$$H''(s) = \frac{K_{\nu}K_{d}(s\tau_{2}+1)/\tau_{1}}{s^{2} + s(\frac{K_{\nu}K_{d}\tau_{2}}{\tau_{1}}) + \frac{K_{\nu}K_{d}}{\tau_{1}}}$$

(4)

However, it is possible to rewrite the transfer function equation (4) in terms of natural frequency  $(\omega_n)$  and damping ratio  $(\zeta)$  of the loop. The parameters  $\omega_n$  and  $\zeta$  for the active filter are given by:

$$\omega_n = \left(\frac{K_v K_d}{\tau_1}\right)^{\frac{1}{2}} \tag{5}$$

$$\xi = \frac{\tau_2}{2} \left( \frac{K_v K_d}{\tau_1} \right)^{\frac{1}{2}} = \frac{\tau_2}{2} \omega_n \tag{6}$$

$$\tau_1 = R_1 C \tag{7}$$

$$\tau_2 = R_2 C \tag{8}$$

Rewriting equation (4) in terms of parameters  $\omega_n$  and  $\zeta$ , we have:

$$H''(s) = \frac{s2\xi\omega_n + \omega_n^2}{s^2 + 2\xi\omega_n s + \omega_n^2}$$

(9)

After the filter process, the PLL has conditions to work right.

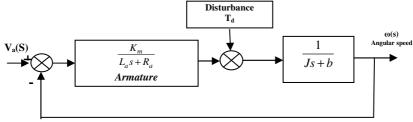

The mathematical equations of a DC motor, in terms of transfer functions, are divided into one transfer function of armature and one transfer function of mechanical inertia equation, according to Ogata. Equation 10 shows the transfer function of armature that is given by:

$$T_m(s) = \frac{K_m}{L_a s + R_a} \tag{10}$$

The transfer function of mechanical inertia is given by:

$$T_i(s) = \frac{1}{Js + b} \tag{11}$$

Figure 9 shows the block diagram of a DC motor with the equations (10) and (11) in the presence of a disturbance. This paper uses a constant disturbance as a representation of environment variability that affects the armature.

Figure 9. DC Motor Block Diagram.

#### 5 Results

The system of Figure 7 was simulated in a Matlab/Simulink environment. The parameters used in the DC motors were:

- Km = 5 N.m/A

- La = 0.1 miliH

- Ra = 3 Ohm

- J = 0.001 N.m.s2

- b = 0.01 N.m.s

- Td1 = 0.5 N.m (disturbance in DC Motor 1)

- Td2 = -0.3 N.m (disturbance in DC Motor 2)

The PID parameters were:

- Kp = 3

- Ti = 0.04

- TD = 0.01

The PLL parameters were:

- ωn= 224 rad/s

- $\zeta = 0.04$

- Kvco = 1

- Kd = 2.5

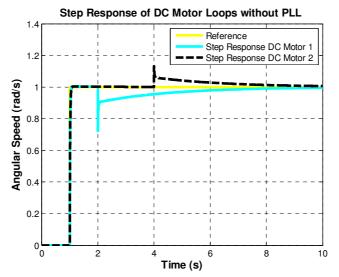

First, we analyzed the step response of the system; i.e., the reference signal for both control loops is a step signal with amplitude of 1 rad/s. The step was applied in t=1 second. After that, the disturbance in DC motor 1 was applied in t=2 seconds and the disturbance in DC motor 2 was applied in t=4 seconds. So, DC motor 1 received a load (disturbance) in 2 seconds and DC motor 2 received a load in 4 seconds.

Figure 10 shows the step responses of both DC motors without PLL actuation.

Figure 10. Step Responses of DC Motor Loops without PLL.

In Figure 10, the continuous yellow line is a reference signal (step), the continuous cyan line represents the step response of DC motor 1 and the dashed black line represents the step response of DC motor 2. We can observe in Figure 10 that the angular speeds of DC motors suffer skews caused by loads (disturbances).

To reduce, or even eliminate, this de-synchronization between angular speeds and angular positions, we proposed to put a a PLL control between the control loops. In this scheme, when a phase skew is detected, the PLL actuate in the DC motors. The idea is to use a PLL to synchronize the angular speeds.

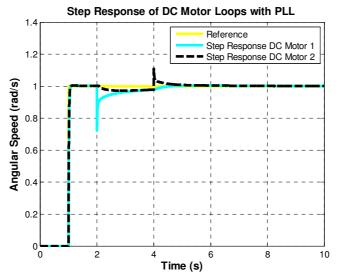

Figure 11 shows the step responses of both DC motors with PLL actuation.

Figure 11. Step Responses of DC Motor Loops with PLL.

In Figure 11, the continuous yellow line is a reference signal (step), the continuous cyan line represents a DC motor 1 and the dashed black line represents a DC motor 2, with PLL actuation. We can observe in Figure 10 that the angular speeds of DC motors suffer skews in each instant of load (disturbance). However, now both DC motor loops are coupled by a PLL control between loops. Thus, if a phase skew between output signals (angular speeds) is detected, the PLL actuate in the loops. This actuation reduces the de-synchronization of angular speeds, and hence the skew in position.

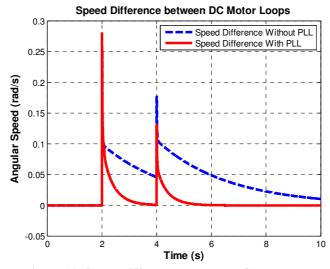

Figure 12 shows the angular speed difference between the loops. The dashed blue line is the difference without PLL and the continuous red line is the difference with PLL. We observe that a system with PLL decreases the speed difference faster than a system without PLL.

Figure 12. Speed difference between DC Motor Loops.

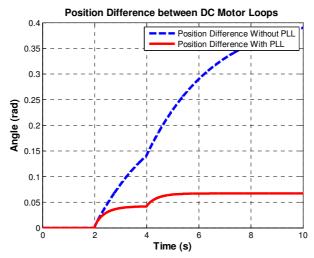

Similarly, Figure 13 shows the angular position skew between the loops with PLL and without PLL. We observe that the PLL loop drives the angular position difference to a constant value, i.e., in spite of the position difference do not go to zero, the position difference is locked in a determined precision to be chosen by design.

Figure 13. Position difference between DC Motor Loops.

The system with PLL control presents a better performance in terms of phase synchronization in this case in comparison with a system without PLL.

### 6 Conclusions

The phase synchronization problem appears in various contexts: control, navigation, computing, communications, control of vehicles, power generation. These and many other areas where accurate phase or time synchronization is a determining factor to the correct operation of the system, can apply the PLL technique.

The PLL provides a good technique to achieve phase or time synchronization and has been proved efficient to achieve the synchronization reducing the skew due to environment variability.

The PLL can be used to synchronize the phase of the controlled oscillator to the phase of a reference signal. There is a lot of applications that make use of the PLL technique to control DC motors with one reference. Sometimes, two or more different control loops need to synchronize their outputs in phase. This paper applied the PLL technique to synchronize two independent DC motor loops under environment variability. More analysis is necessary and still is in progress, in the general case.

The results of this case suggest that: 1) The PLL is a good technique to reduce or even eliminate the unwanted effects of skews in phase between distinct control loops; 2) the PLL control helps the control to establish angular speed synchronization of DC motors; 3) the PLL had the fastest response and converged rapidly for its reference reducing the skew, without trouble to converge; and 4) the PLL can contribute to high levels of performance and reliability of reconfigurable controls of aerospace, automotive and power systems.

## Acknowledgments

Both authors thank the National Institute for Space Research - INPE of Brazil, its Course and Division of Space Mechanics and Control-CMC/DMC for supporting them during the writing of this paper. The first author acknowledges CAPES and CNPQ financial support during his Master and Ph.D. Programs and the writing of this paper.

#### References

SAE, "Certification Considerations for Highly-Integrated or Complex Aircraft Systems," Aerospace Recommended Practice ARP-4754, SAE, Nov. 1996.

Meyr, H. and Ascheid, G., "Synchronization in Digital Communications: V1-Phase-, Frequency-Locked Loops, and Amplitude Control", vol. 1, USA: John Wiley & Sons, 1990, ISBN --471-50193-X (v. 1).

Hsieh, G. and Hung, J. C., "Phase-Locked Loop Techniques – A Survey," IEEE Transactions on Industrial Electronics: vol. 43, n. 6, December 1996.

Oklobdzjja, V. G., Stojanovic, V. M., Markovic, D. M. and Nedovic, N. M; Digital System Clocking: High-Performance and Low-Power Aspects. Holboken, New Jersey: John Wiley & Sons, 2003.

- Djamito, W. and Sutopo, B., "Speed Control DC Motor under Varying Load Using Phase-Locked Loop System," Proceedings of the International Conference on Electrical, Electronics, Communication and Information, Jakarta, March 2001.

- Suri, N.; Hugue, M.M.; and Walter, C.J.; "Synchronization Issues in Real-Time Systems," Proceedings of the IEEE, vol.82, no.1, pp.41-54, Jan 1994 doi: 10.1109/5.259425.

- Kihara, M.; Ono, S.; Eskelinen, P., "Digital Clocks for Synchronization and Communications", Boston: Artech House, 2003, ISBN: 1-58053-506-2.

- Ogata, K.; "Engenharia de Controle Moderno". 3rd. ed. Rio de Janeiro, RJ: Prentice-Hall do Brasil Ltda., 1997. 813p. ISBN: 85-7054-074-4.

- Machida, H. and Kobayashi, F., "PLL/PID Motor Control System by Using Time-Domain Operation of PWM Signal" Proceedings of SICE Annual Conference, Kagawa, Japan, September 2007.

- Oliveira Junior, E.M.; Souza, M.L.O. "The use of PLL Techniques for Accurate Time or Phase Synchronization in Aerospace and Automotive systems", Proceedings of SAE Brasil 2011, São Paulo, Brazil, 2011, ISBN:2011-36-0179.